名称:2024南昌国际半导体及集成电路博览会

时间:2024年9月27-29日

地点:南昌绿地国际博览中心

展馆详细地址:南昌市红谷难区怀玉山大道1315号

来源:内容由半导体行业观察(ID:icbank)编译自anandtech,谢谢。

客户对 AI 和 HPC 处理器的需求正在推动先进封装技术的广泛使用,特别是台积电的晶圆基板芯片 (CoWoS) 服务。就目前情况而言,台积电仅勉强满足当前对这种封装方法的需求——更不用说未来的需求——这就是为什么该公司去年宣布计划到 2024 年底将 CoWoS 产能增加一倍以上。

但事实证明,只是产能一旦增加一倍是不够的,全球最大的芯片代工制造商将不得不继续快速扩大规模。

在上周的欧洲技术研讨会上,台积电宣布计划以超过 60% 的复合年增长率 (CAGR) 扩大 CoWoS 产能,至少到 2026 年为止。因此,到 2026 年底,台积电的 CoWoS 产能将比 2023 年水平增加四倍以上那个时期。请记住,台积电正在准备 CoWoS 的其他版本(即 CoWoS-L),该版本将能够构建多达 8 个掩模版尺寸的系统级封装 (SiP),因此在三年内将 CoWoS 容量增加四倍可能仍然无法实现足够。

好消息是,各种第三方场外组装和测试 (OSAT) 提供商也在扩大其类似 CoWoS 的产能,因此对先进封装的需求并不是台积电面临(或解决)的问题。

CoWoS 并不是台积电希望快速扩大产能的唯一先进封装技术生产线。该公司还拥有集成芯片系统 (SoIC) 3D 堆叠技术,该技术的采用率有望在未来几年内不断增长。为了满足对其 SoIC 封装方法的需求,台积电将在 2026 年底之前以 100% 的复合年增长率扩大 SoIC 产能。因此,到 2026 年底,SoIC 产能将比 2023 年的水平增长八倍。

总体而言,台积电本身预计,未来几年用于人工智能和 HPC 等高要求应用的尖端 SiP 将同时采用 CoWoS 和 SoIC 3D 堆叠技术,这就是为什么它需要增加这两种方法的容量才能构建这些高度复杂的处理器。

值得一提的是,晶圆代工龙头台积电在2024年年初的首场法说会中曾指出,CoWoS、SoIC等先进封装需求非常强劲,未来数年至少将以CAGR 50% 速度成长。法人则看好,随着台积电持续扩大先进封装产能布局,相关台系设备商今、明(2024~2025)年都将会是丰收年。

台积电于法说会上定调今年美元计价营收将成长逾两成,并多次强调已看到AI将为驱动公司成长的重要动能,这让半导体芯片制程与封装价值的提升,除有扩充3纳米、2纳米先进制程的规画,也预期今年CoWoS会扩一倍,但因扩增后仍供不应求,2025年还会继续扩产。

尽管台积电未详述详细扩产数据,但半导体业界消息则透露,CoWoS今年底月产能可望达到3~3.4万片,2025年将增至4.4~4.6万片;SoIC部份,近期也进一步上修产能规划,去年底SoIC月产能约2000片,目标今年底达近6000片,2025年月产能目标再倍增逾1倍,有可能达到1.4~1.5万片水准。

CoWoS是什么?

AI需求爆发,台积电先进封装CoWoS产能供不应求,台积电总裁魏哲家强调,CoWoS需求「非常、非常(very very)」强劲,台积电将在2024年扩充超过两倍的CoWoS产能,但还是无法满足AI客户的半导体需求。

魏哲家认为,客户的成功仍是台积电的首要任务,无论客户是否找上其他CoWoS代工厂都不是台积电所要担心的。同时,台积电也会基于长期的伙伴关系持续给予所有客户支援,而非仅聚焦在单一大客户。

对于扩充CoWoS产能,《路透社》先前引用知情人士来源指出,台积电考虑在日本建立先进封装能力,其中一个选择是将CoWoS封装技术带到日本。目前,台积电的CoWoS产能全都在台湾。

报导指出,此举将为正在为加紧半导体产业竞争力的日本,增添动力。不过由于审议还在初步阶段,因此投资规模与时程还不确定。对此,台积电拒绝置评。

另外,台积电确定进驻嘉义科学园区。行政院副院长郑文灿3月18日指出,台积电两座CoWoS先进封装厂落脚嘉义,预计5月初动工。

究竟CoWoS是什么,以下文章带您一次看懂:

AI概念股大爆发,晶圆龙头台积电除成为最大受益者外,先进封装CoWoS产能更是供不应求。应用在AI的先进芯片,需同时达到高速和节能以及成本控制,CoWoS是当前重要的解决方案,台积电董事长刘德音会也在六月股东会上表示,AI大幅带动了先进封装的需求。

国内能同时做到生产先进制程和封装的厂商仅有台积电一家,高品质且一条龙的服务成为AI浪潮下的直接受益者。究竟什么是CoWoS?台积电当前产能状况如何?又有哪些周边厂商值得关注呢?

那么CoWoS先进封装是什么?

CoWoS可以分成「CoW」和「WoS」来看。

「CoW」指的是「Chip-on-Wafer」,指的是芯片堆叠;「WoS」指的是「Wafer-on-Substrate」,则是将芯片堆叠在基板上。简单来说,CoWoS指的就是把芯片堆叠起来,然后封装于基板上,以此来减少芯片需要的空间,同时也可以减少功耗和成本。

CoWoS的出现,也延伸了摩尔定律的寿命。由于芯片的微缩将导致芯片成本增加,每两年节省一半成本的定律将不复存在,然而透过CoWoS,能够将不同制程的芯片封装在一起,例如5纳米的GPU和12纳米的射频芯片,借此达到加速运算但成本可控的目的。

CoWoS封裝是什麼?

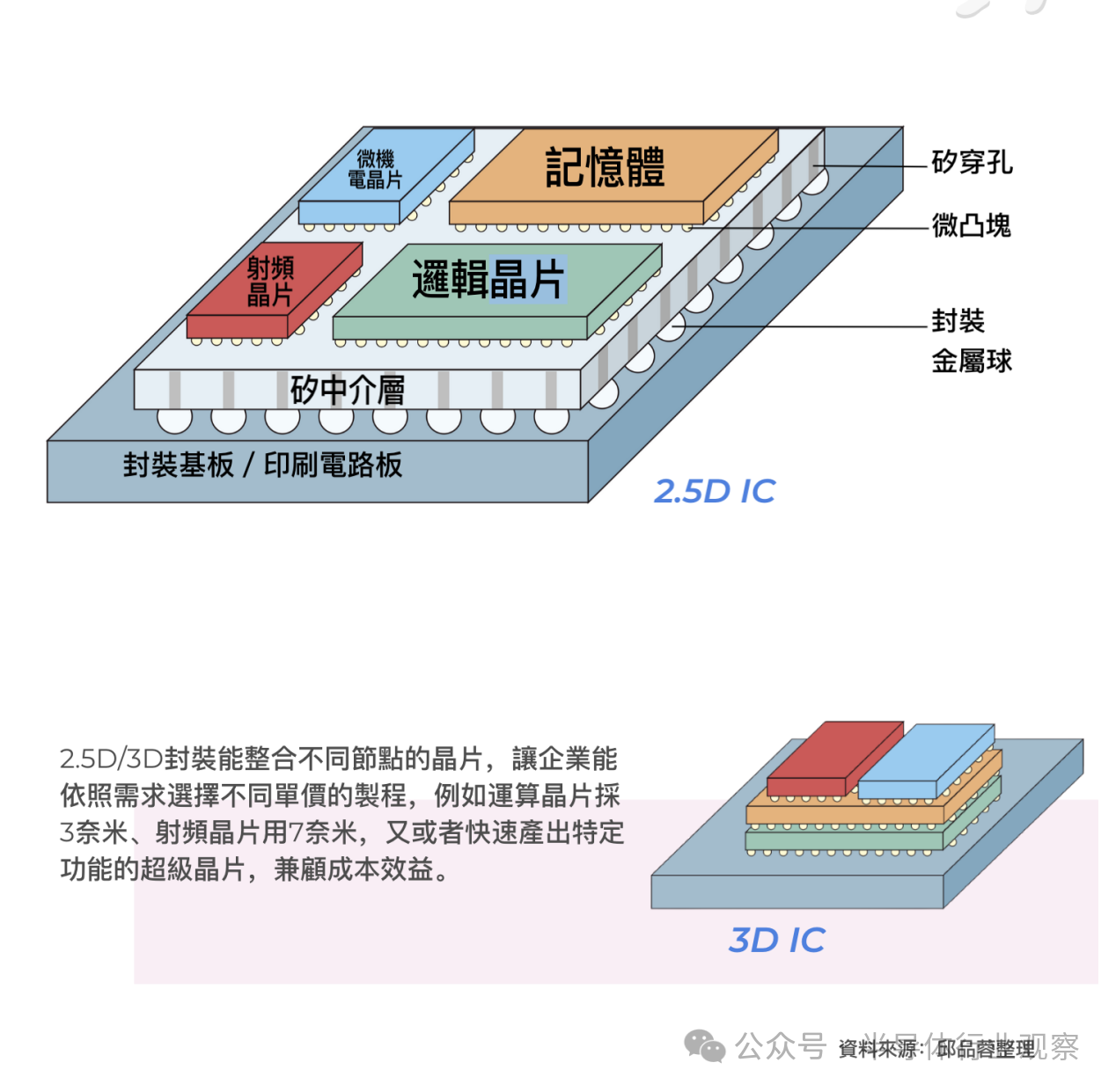

CoWoS有2.5D和3D封装版本(下图)指将不同功能的模块做成小芯片(chiplet),全部封在1块芯片内,因此可看到1块芯片内不仅有逻辑芯片,还包含存储器、射频芯片和微机电芯片,不过只服务7纳米以下制程。诸如苹果、超微和英伟达等,都已在效能强大的高阶产品采用先进封装。

以台积电来说,当前先进封装服务的对象为下单7纳米以下制程客户,换句话说,如苹果(Apple)、英伟达(NVIDIA)和超微(AMD)这样的顶级客户群才能够下单CoWoS。

CoWoS仍存有一些待解决的问题,例如由于芯片堆叠后所产生的等热问题,或良率提升等等,都让CoWoS在生产上出现一些障碍。除此之外,以现阶段而言台积电CoWoS供应量还太少,野村证券就指出,台积电CoWoS产能,是导致当前AI芯片出货量卡关的主要原因。

台积电总裁魏哲家在上周第二季的法说表示,接下来CoWoS的需求几乎是双倍成长,台积电也正积极扩充产能当中。

免责声明:来源标记为网络的文章其原创性及文中陈述文字和内容未经我司证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺请读者仅作参考并请自行核实相关内容,版权归原作者所有,如有侵权请联系我们删除。